【課題探求実習セミナー】プログラマブルICによる論理回路設計

verilogシミュレーションの練習

ここまでの授業では、回路をverilog言語で設計し、CPLDに直接書き込んで動かした。

CPLDの場合は、自分で何度も書き込み直しが可能であるが、もっと大規模なASICなどでは、

書き直しが利かないため、設計段階で回路の動作をよく検証する必要がある。

回路シミュレーションが、回路設計の重要な工程なのである。

CPLDやFPGAのように書き換えが可能であっても、思った通りの動作が実現できていないとき、

バグを理解するためにシミュレーションが役に立つことは多い。

実物がその場になくても回路の動作を検証できるため、シミュレーションの仕方を習得

しておくことは便利である。

ここでは、LED4個を4ビットカウンタとしてピコピコさせる練習問題を例として、

XilinxのISE WEB PACKでのverilog シミュレーションの仕方を習得する。

LED4個を、4ビットカウンタとしてピコピコさせる

verilog source

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 13:05:18 05/17/2016

// Design Name:

// Module Name: LED4bitpicopico

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LED4bitpicopico_verilog(

input CLK,

input RESET_,

output [3:0] LEDdrv);

reg [3:0] OUT;

integer COUNTER;

// カウンタが5になったら次のクロックで1にもどして再び5まで数える(周期5クロック)。

// 5クロックくるたび一度、OUTは繰り上げられている。

// LEDdrvはOUTがそのままつながっているので、LED[3:0]は、5クロックごとに

// 繰り上がる4ビットの信号となっている。

always @ (posedge CLK) begin

if (RESET_==0) begin

COUNTER <=0;

OUT<= 4'b0000;

end

else begin

// if (COUNTER==50000000) begin // 50000000 CLK = 1 sec (CLK: 20 MHz)

if (COUNTER==5) begin // for simulation example

OUT[3:0] <= OUT[3:0] +1;

COUNTER <= 1;

end else begin

COUNTER <= COUNTER +1;

end

end

end

assign LEDdrv= OUT;

endmodule

ピン配置(ucfファイル)

NET "CLK" LOC = "P1";

NET "RESET_" LOC = "P7";

NET "LEDdrv[0]" LOC = "P31";

NET "LEDdrv[1]" LOC = "P32";

NET "LEDdrv[2]" LOC = "P33";

NET "LEDdrv[3]" LOC = "P34";

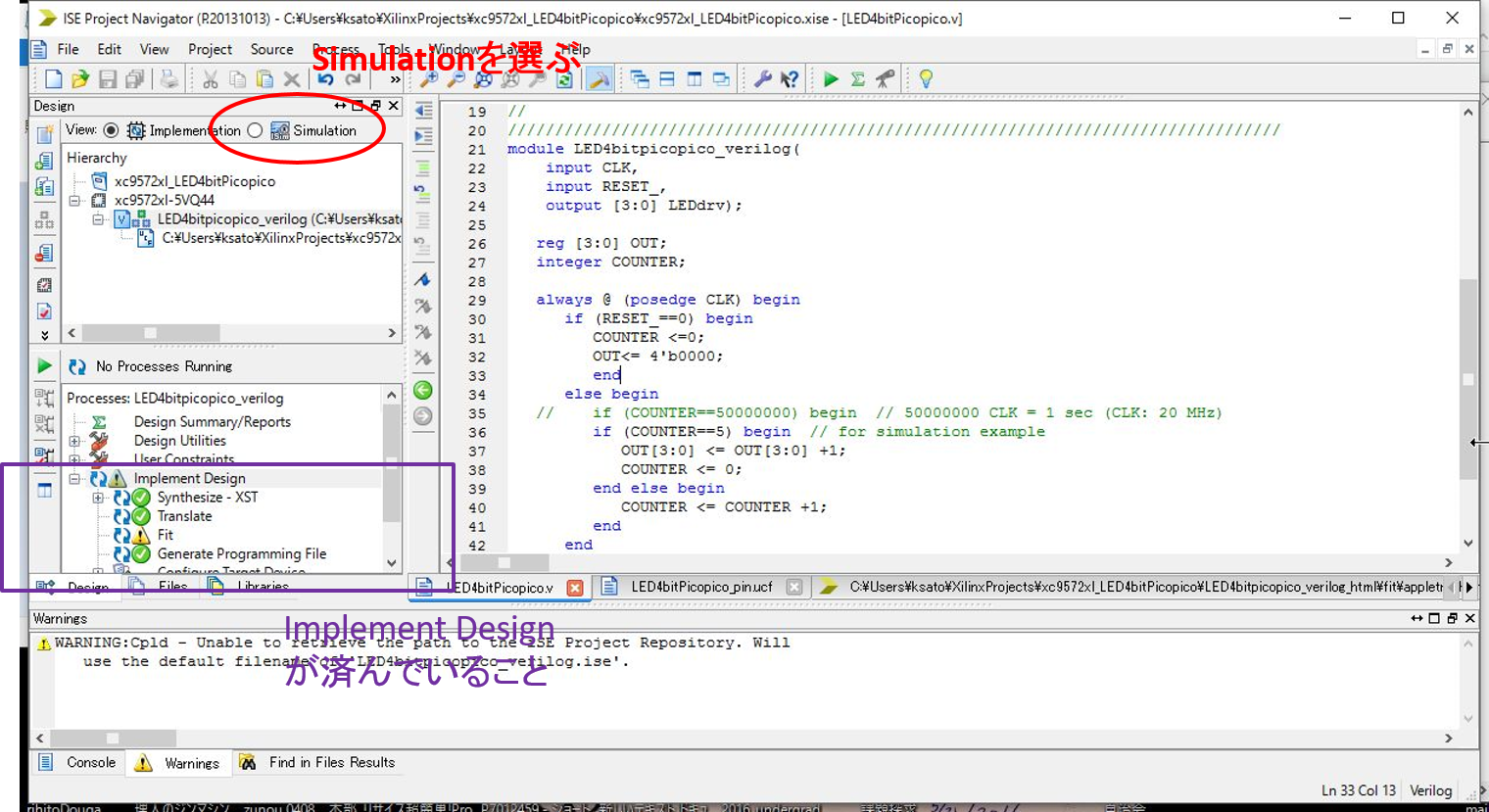

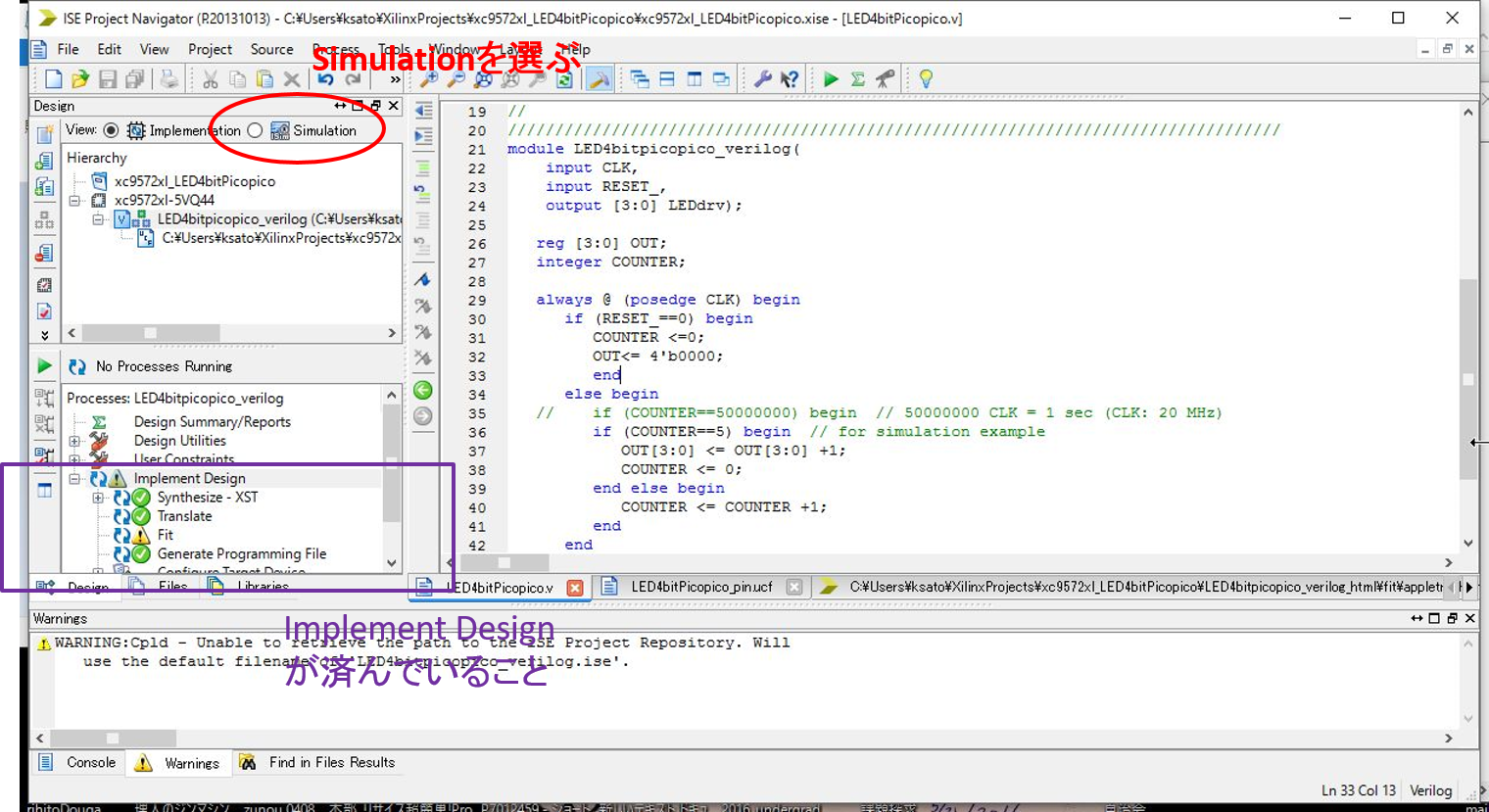

source codeとピン配置が決まったら、

"Implement Design"を済ませておく。

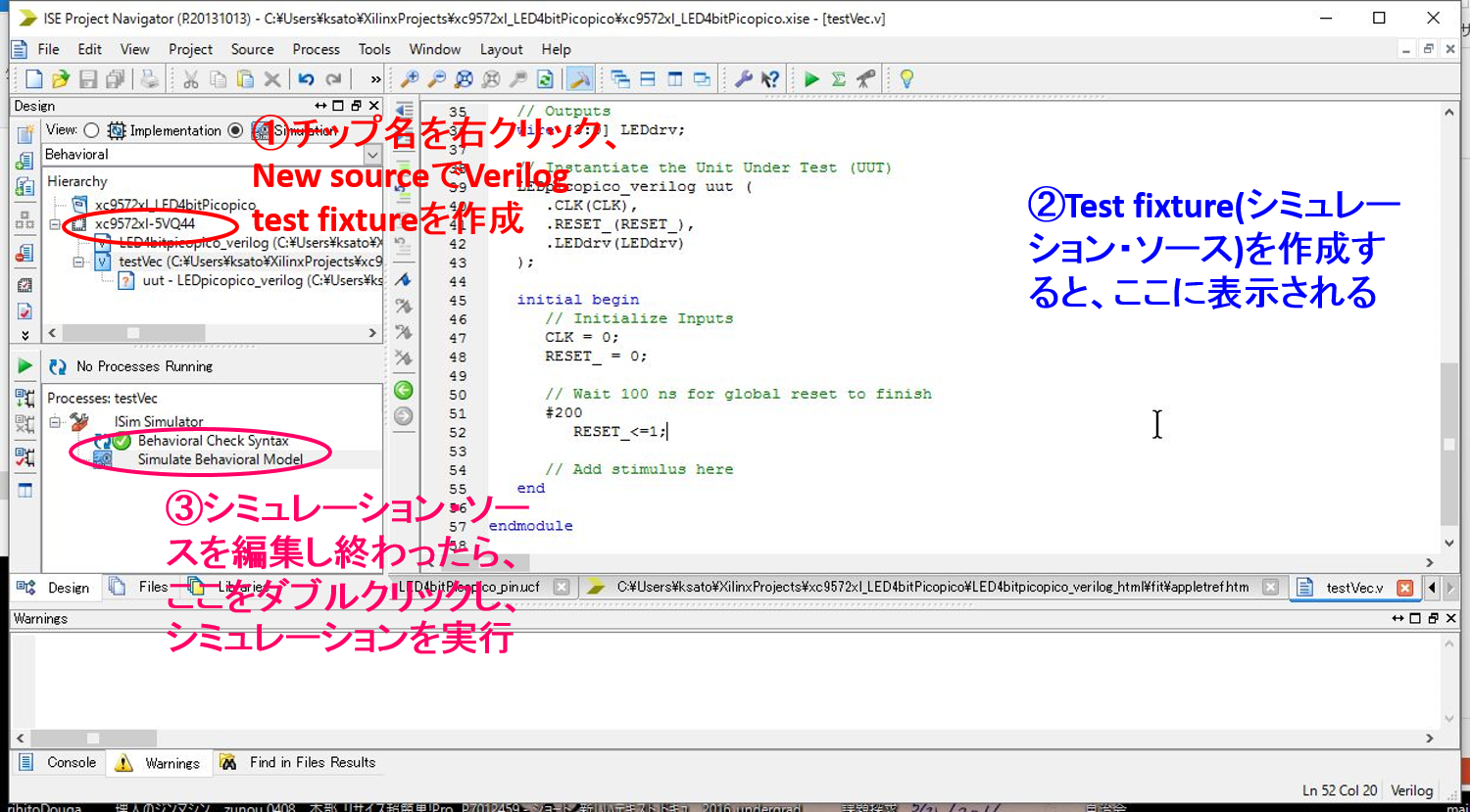

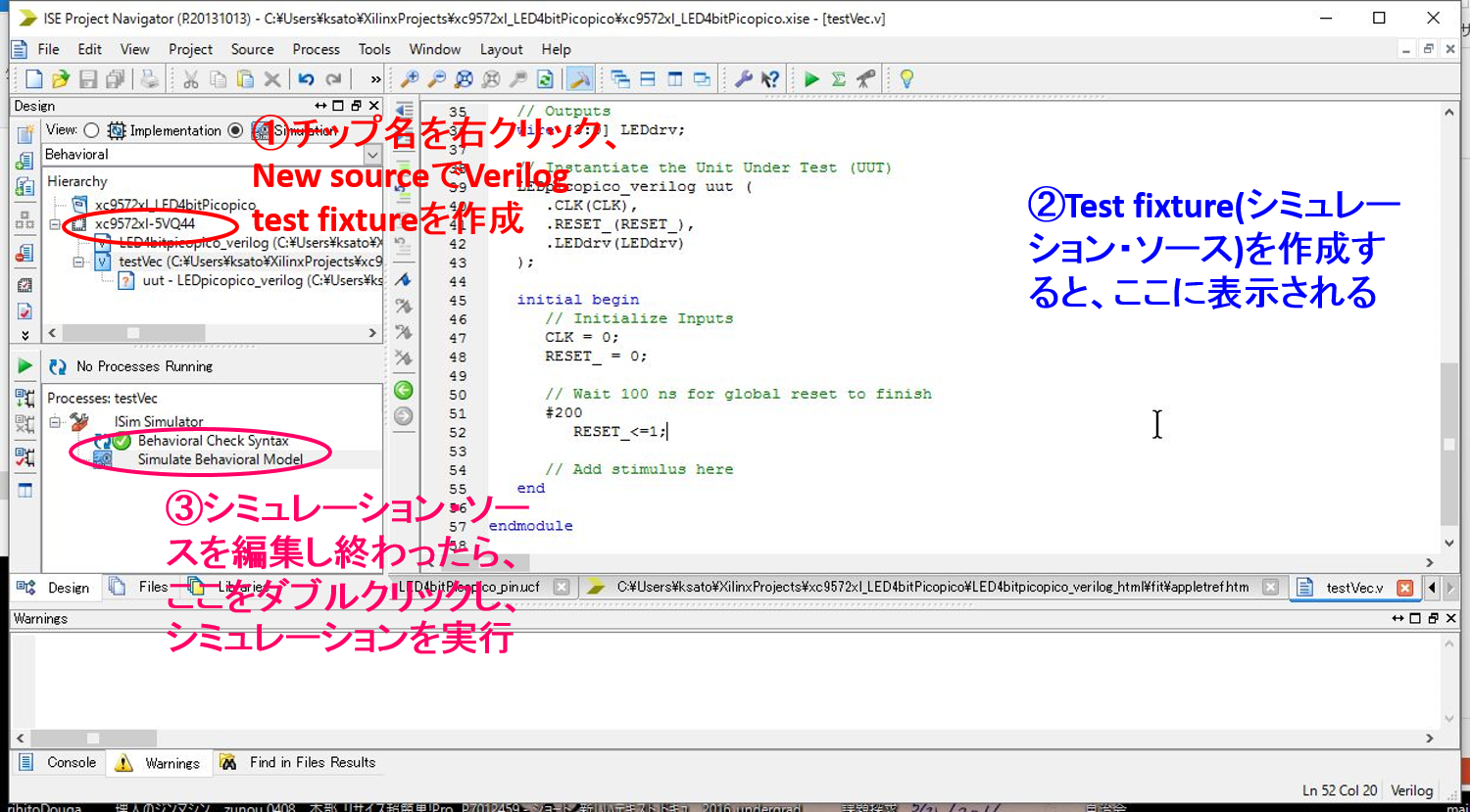

verilogシミュレーションのソースコード

Simulationのメニューで、

- チップ名を右クリック→New source

→verilog test fixtureを選択、ファイル名を入力

を行う。

シミュレーション信号を定義するための

verilog ソースコードが生成される。

これを、以下に置き換える。

// 時間の単位 1ns / 時間の精度 1ps

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 17:59:20 06/07/2016

// Design Name: LEDpicopico_verilog

// Module Name: C:/Users/ksato/XilinxProjects/testProject/testVec.v

// Project Name: testProject

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: LEDpicopico_verilog

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module testVec;

// Inputs

reg CLK;

// CLK信号は、いつも10 nsごとに、反転する。

always #10

CLK <= !CLK;

reg RESET_;

// internal lines and registers

// Outputs

wire [3:0] LEDdrv;

// Instantiate the Unit Under Test (UUT)

// LED4bitPicopicoモジュールの入出力 .CLK, .RESET_, .LEDdrv

// に、シミュレーション信号であるCLK, RESET_, LEDdrvを割り当てる

LED4bitPicopico_verilog uut (

.CLK(CLK),

.RESET_(RESET_),

.LEDdrv(LEDdrv)

);

// シミュレーションでの初期値をあたえる。

initial begin

// Initialize Inputs

CLK = 0;

RESET_ = 0;

// 200 nsたったら、RESET_を終える(RESET_は負論理)

#200

RESET_<=1;

// Add stimulus here

end

endmodule

編集ができたら、

Behavioral Check Syntaxをダブルクリックして、文法チェック。

それが終わったら、

Simulate Behavioral Modelをダブルクリックして、

シミュレーションを走らせてみよう。

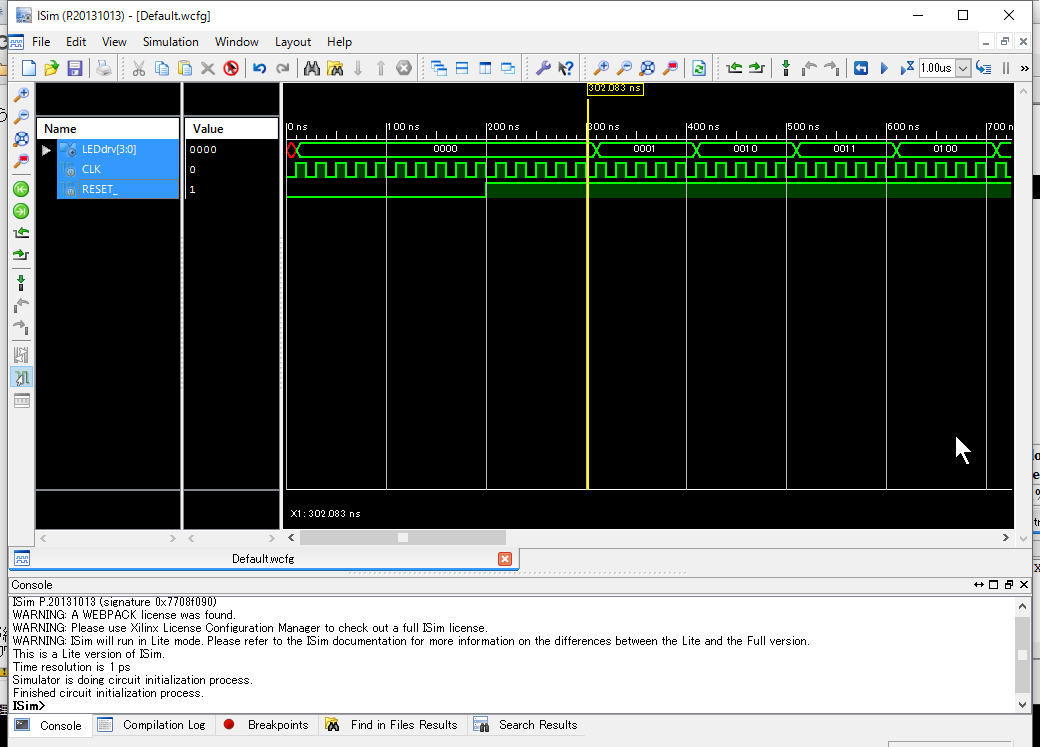

シミュレーションの結果

以下のようなシミュレーション結果が表示される。

RESET_が終わって(1になる)から、回路はクロックを数え始める。

verilog sourceのとおりに、回路はクロックを5回数えるたびにLEDdrv[3:0]を

繰り越しているカウンタになっているだろうか。

CPLDに実装してみよう

シミュレーションで確認できたら、CPLDに実際に実装してみよう。

ただし、5クロック=5/50MHz= 100 ns でLEDがピコピコしてもわれわれの

目には見えない。

ソースコードで数えているクロック数を変更して、1秒ごとに繰り上がるカウンタ

を実装してみよう。

本練習問題では、CPLDボード上に配置されているLEDを光らせるようにピン配置を設定している。

LEDpicopico のシミュレーション

前回のLEDpicopicoの例題(LED一個の例題)をシミュレーションするにはどうするか。

LEDpicopicoは、外部入力がCLKしかないので、COUNTERをリセットする方法がない。

COUNTERの初期値がきまらないかぎり、意味のあるシミュレーションを行うことができない。

各自、どうするのがよいか考えてみてほしい。