本授業では、日昇テクノロジーのCPLD開発キットを用いて、 プログラマブルICを用いた論理回路設計を行う。 開発キットはXilinx社製CPLD XC9572を搭載している。

このページでは、verilog言語で記述したサンプルコードを使用しながら 例題をこなすことにより、 回路を設計、コンパイルし、設計をICに実装する全体の流れを習得できるように 記述した。 本例題では、ブレッドボード上に配置したLEDの点灯を制御してみる。 設計データのICへのダウンロードはUSB-JTAGで行うが、そのケーブル接続の仕方等の 詳細も記述している。

本ページでははじめに、ISE WebPACKのダウンロード、インストールの仕方も示しているので、 参考にしてほしい。 なお、ISEはWindows版とLinux版しかないので、持っていない人は研究室のPCを借りて作業する。

目次:

ロジックICは、一般には「標準IC」と、ユーザが自由に機能を設計して 使用できるカスタムICに大別できる。 標準ICは機能が決まっており、ユーザは基板上にいくつかのICを配置し、 これらの間を配線することで目指す機能を実現する。 カスタムICの場合は、IC内部のゲート(ANDやORの素子)間の配線をユーザが設計、実装することで、 目指す機能(の大部分)を一つのICで実現することができる。

カスタムICの中でも、ユーザの設計 をもとに工場で生産した後では機能が変更できないASIC(Application Specific IC) と、ユーザが自前のPCから論理を焼きこむことができる Programmable Logic Device (PLD)がある。 実装できる回路の規模は、PLDよりもASICのほうが大きいが、 PLDは設計のデバッグ、アップデート後の再実装がユーザの 手元で自由に行える分、小回りが利く。 PLDの中でも最大の規模のものがField Programmable Gate Array(FPGA) である。 CPLDはFPGAよりは小規模であり、その分コスト面で安く済む。

標準ICを組み合わせて回路を実装する場合には、回路図を描くことが 回路設計であった。 PLDの設計の場合、Hardware Design Language (HDL)によって回路記述 する場合が多い。 そうして記述したソースコードをコンパイルすることで配線データが 出来上がるが、配線データファイルをICに書き込んで IC内に回路を実装する。 本ページでもverilogHDL言語で回路を記述しているが、HDL言語による回路記述がC言語による プログラミングに非常に似ていることが分かってもらえるかと思う。

本授業ではXilinx社製CPLDを教材として用いる。 CPLDの設計は、Xilinx ISE WebPACKを用いて行う。 ISE WebPACKは、Xilinx社製のFPGAの開発も行なうことができる。

開発キットのマニュアル、データシート等の詳細は以下からダウンロードできる。

各自、自分のPCにISE WebPACKをインストールする。 ISEはWindowsまたはLinuxにしか対応していない。 持っていない人は素粒子実験研究室のWindowsマシンを借りる。

ISE WebPACKは以下のウェブページから無料で配布されている。

http://japan.xilinx.com/products/design-tools/ise-design-suite/ise-webpack.html

インストールの際に、ユーザアカウントを作成することが必要となる。各自、アカウントを作成してソフトウェアをインストールする。

インストール後の問題への対処

Windows 8や10の場合、さまざまな場面でソフトが落ちることがある。その場合、

http://openit.kek.jp/training/2014/fpga/docs/Windows8_trouble.pdf

の【解決法1:64bit 版を動作させる】以下を参考に、libPortability.dllを置き換えることで解決する場合がある。

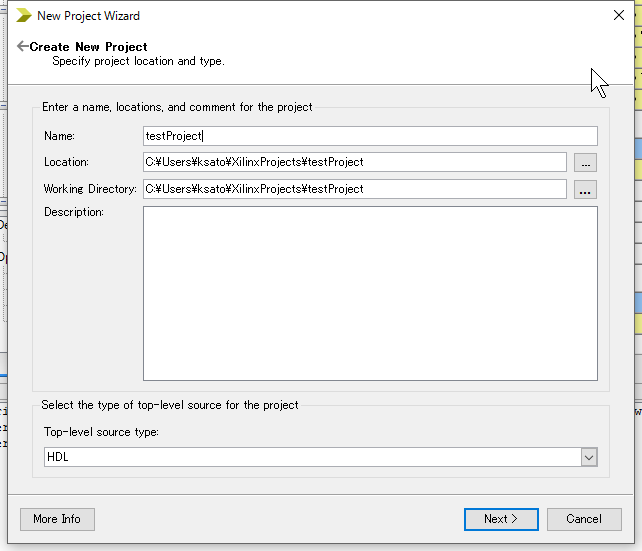

ISE Project Navigator の File タブから New Project を選択。適当なプロジェクト名をNameに入力し、"Next"をクリック。

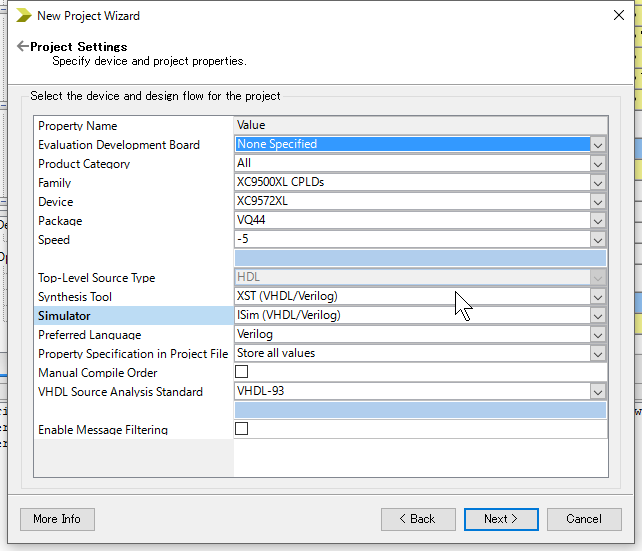

デバイスの選択、記述言語(verilog または VHDL)を選択し、"Next"。

デバイスは、"XC9572XL"、パッケージは"VQ44"を選ぶこと。

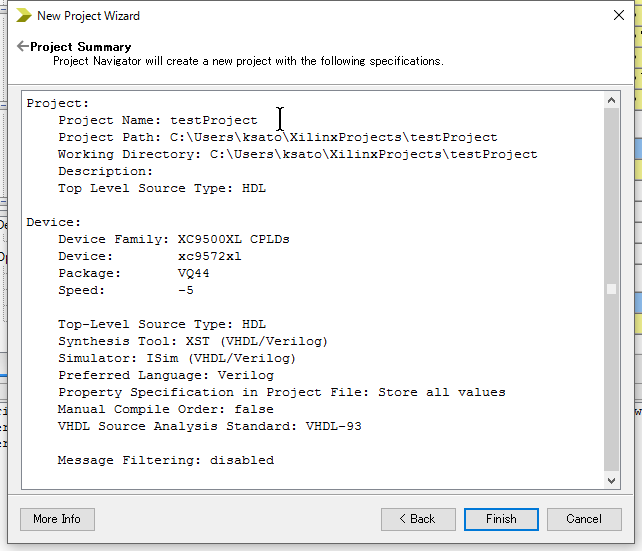

作成するプロジェクトの概要が表示される。"Finish"。

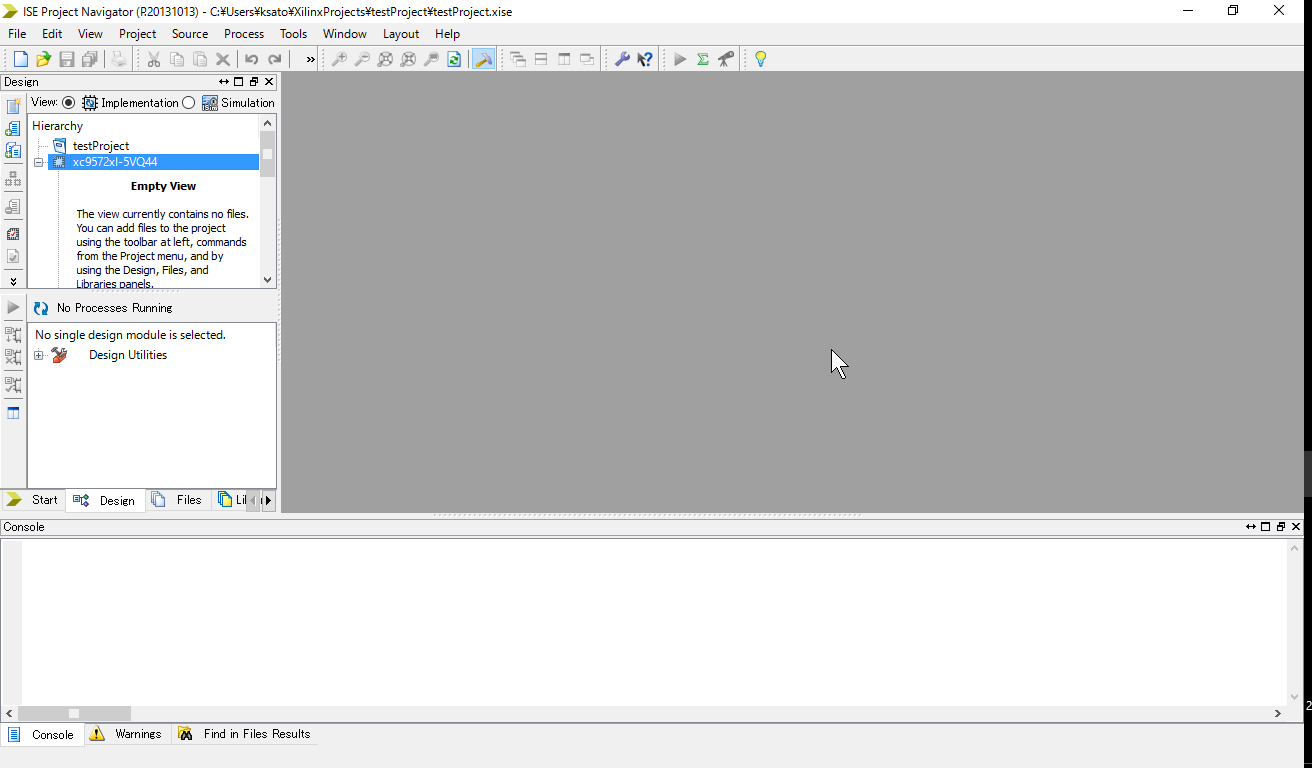

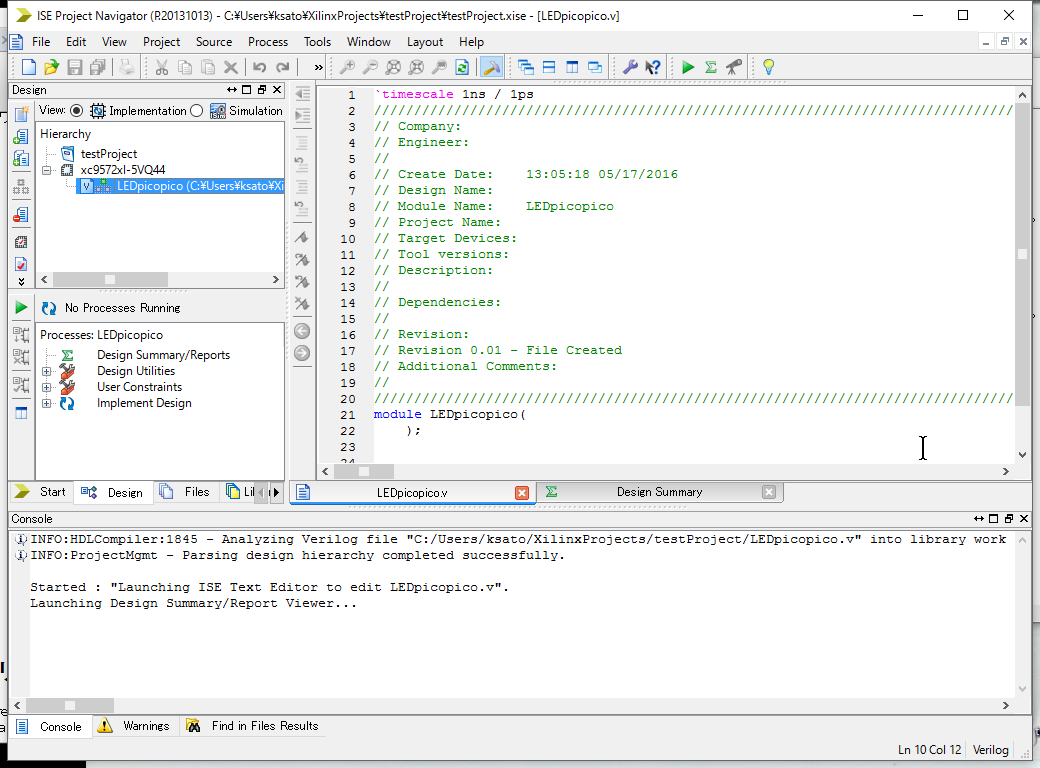

新規プロジェクトが作成され、以下の画面となる。

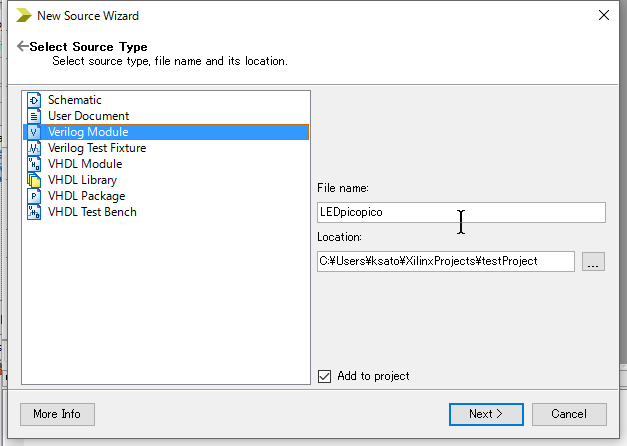

プロジェクト内チップ名(xc9572xl-5VQ44)を右クリックし、"New Source"を選択。

ウィンドウ左側で"Verilog Module"を選択し、右側ウィンドウ"File name"を書き込む。"Next"をクリック。

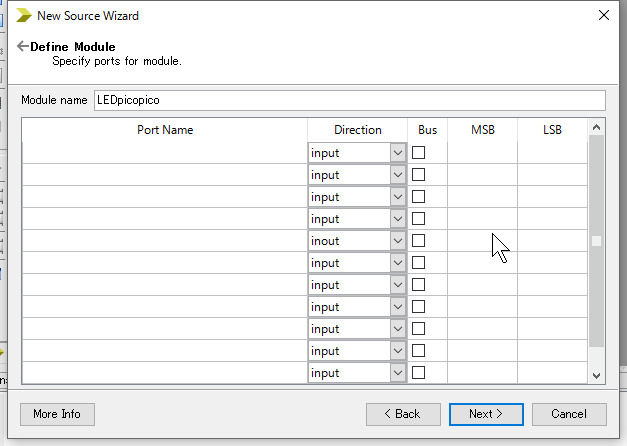

"Next"をクリック。

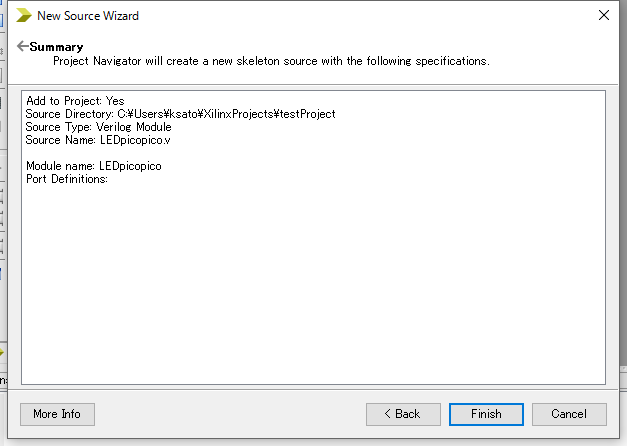

"Finish"をクリック。

新規に、空っぽのverilogソース・ファイル (.v) が生成された。

生成されたverilogソースファイルの内容を全部消去し、 以下を張り付ける。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 13:05:18 05/17/2016

// Design Name:

// Module Name: LEDpicopico

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LEDpicopico_verilog(

input CLK,

output LEDdrv);

integer COUNTER;

always @ (posedge CLK) begin

if (COUNTER==250000000) begin

COUNTER <= 0;

end else begin

COUNTER <= COUNTER +1;

end

end

assign LEDdrv= (COUNTER<50000000);

endmodule

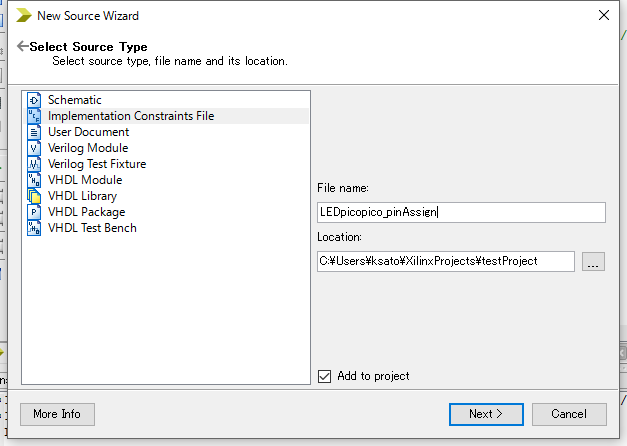

ピン配置を指定するための設定ファイルを生成する。 プロジェクト内チップ名(xc9572xl-5VQ44)を右クリックし、"New Source"を選択。

"Implementation Constrants File"を選択、ファイル名を入力。"Next"。

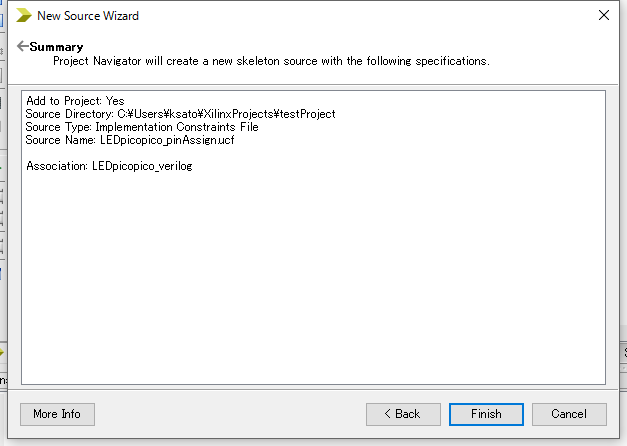

"Finish"。

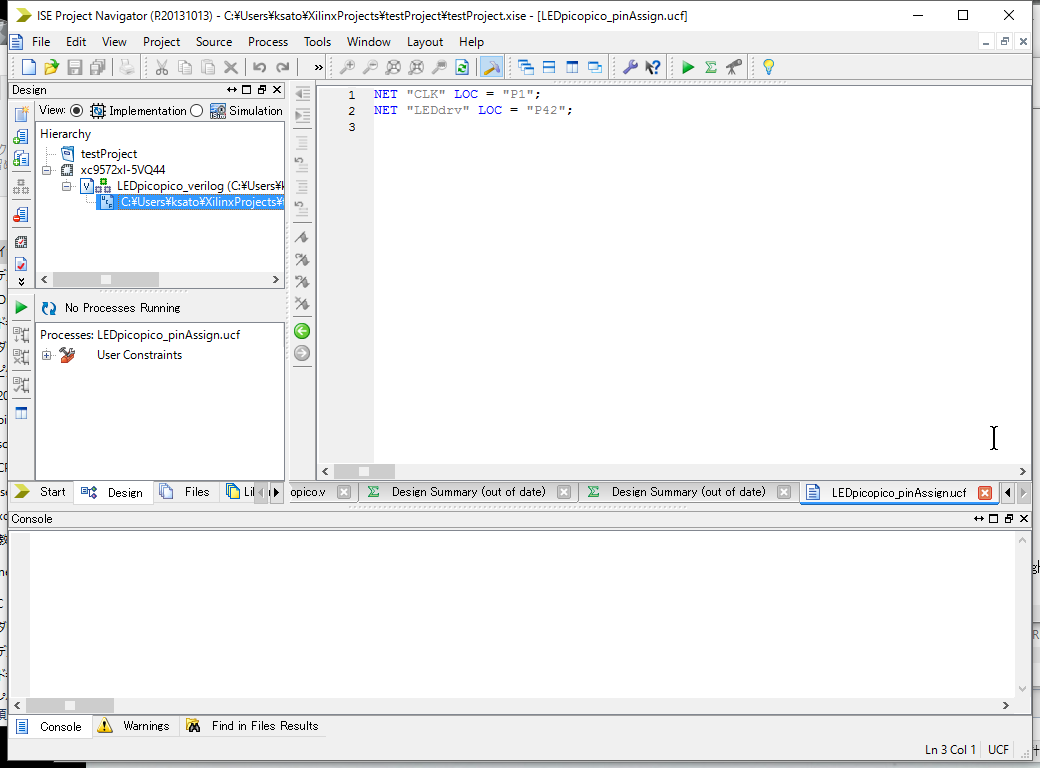

新たに生成された .ucf ファイルを編集する。

.ucfファイルに、以下を張り付ける。

NET "CLK" LOC = "P1";

NET "LEDdrv" LOC = "P42";

LEDやクロックとICのピン配置の対応は、以下の通り。

| クロック (50 MHz) | p1 |

| LED D2 | p34 |

| LED D3 | p33 |

| LED D4 | p32 |

| LED D5 | p31 |

開発キットの基板両脇のI/Oピンから信号の入出力をしたい場合には、 基板に対応するICピン番号が印字されている("p42"など)。

詳しくは、回路図を見る:

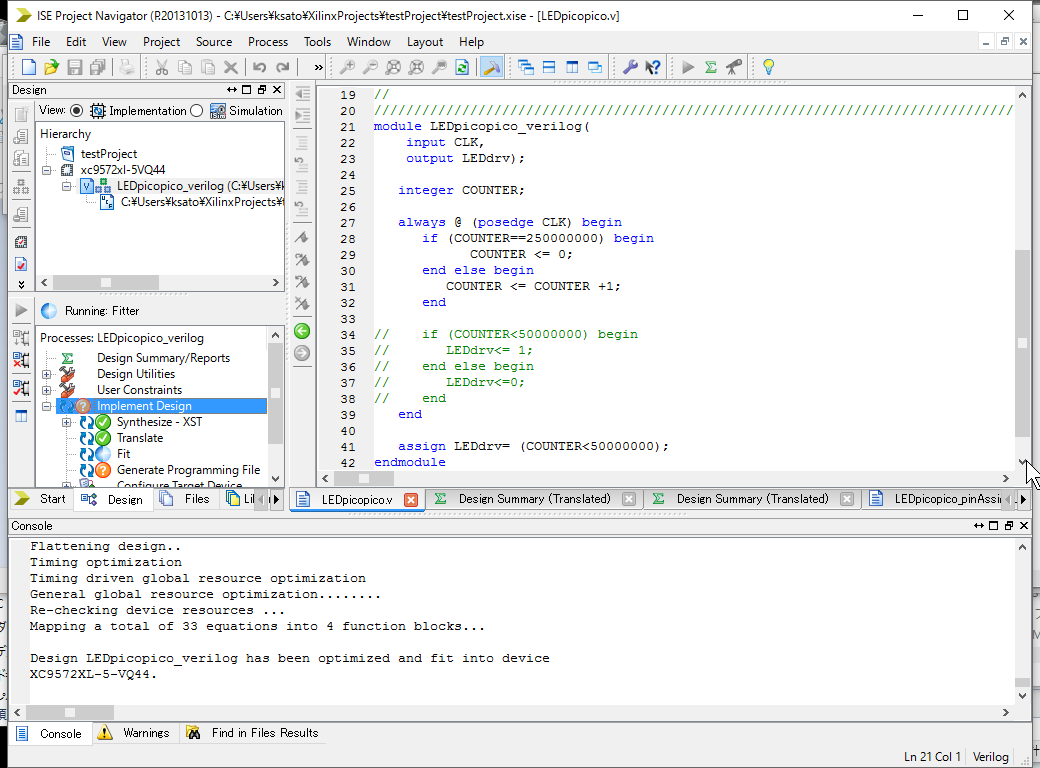

ISEナビゲータ左上フレームで、verilogファイル(以下の図中では、"LEDpicopico_verilog")を選択。 左真ん中のフレーム、"Implement Design"をダブルクリックする。

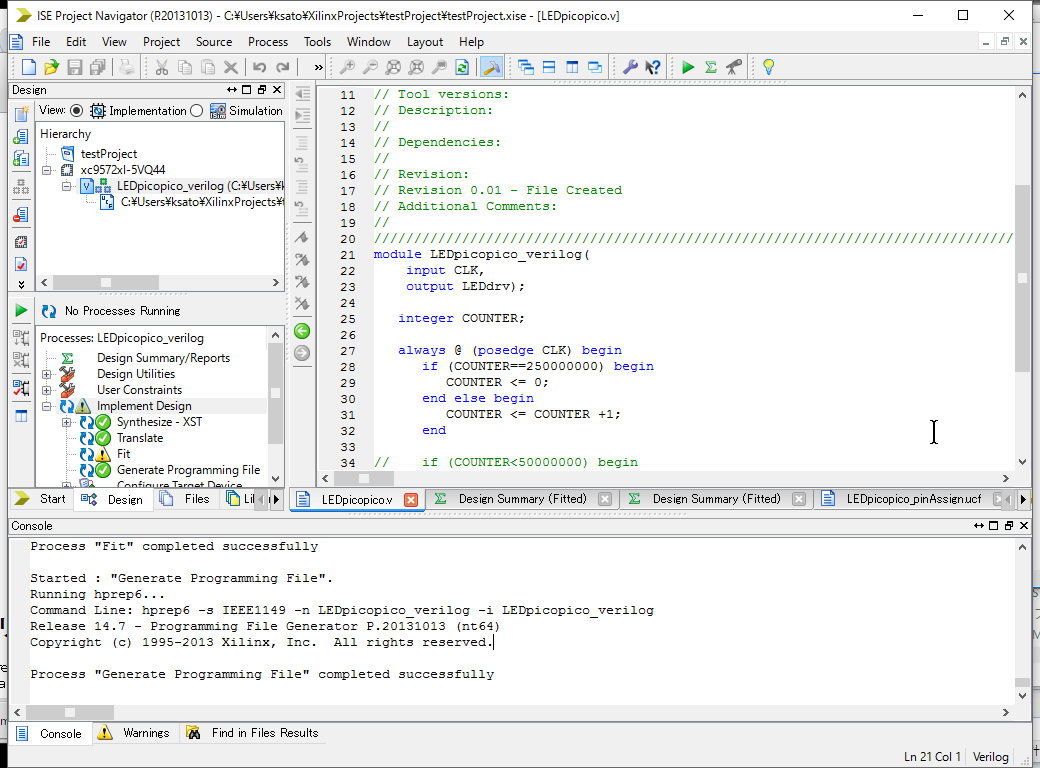

Synthesize, Translate, Fit, Generate Programming Fileの各過程が行われる。 これから行う過程にはオレンジ地に?マーク、 エラーや警告なしに完了した過程に対しては、グリーン地にチェックのロゴが表示される。

警告が起こった場合には黄色地に!が表示される。 ここでは、このまま進める。

"Generate Programming File"が成功すると、プロジェクト・フォルダに .jed ファイルが生成される。

Explorerなどで確認してください。

このファイルが、実際にICに書き込むときのコンフィグレーション・ファイルである。

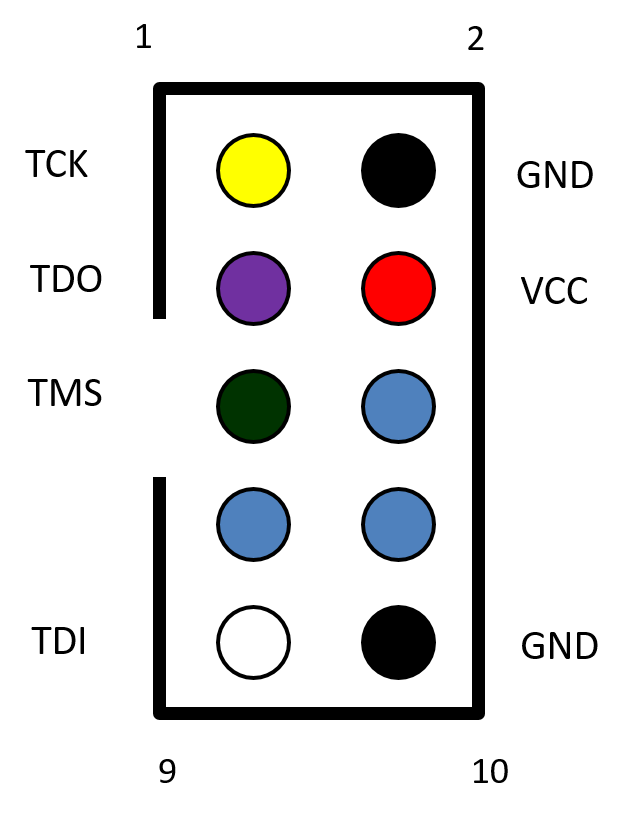

左端がUSBコネクタで、PCに接続する。 右側がJTAG端子である。

JTAGは7個の端子がある。 これら端子を、以下の図を参照しながら、開発ボード上のJTAGコネクタ の各ピンに接続する。 コネクタの空いている部分の向きに注意して接続すること。

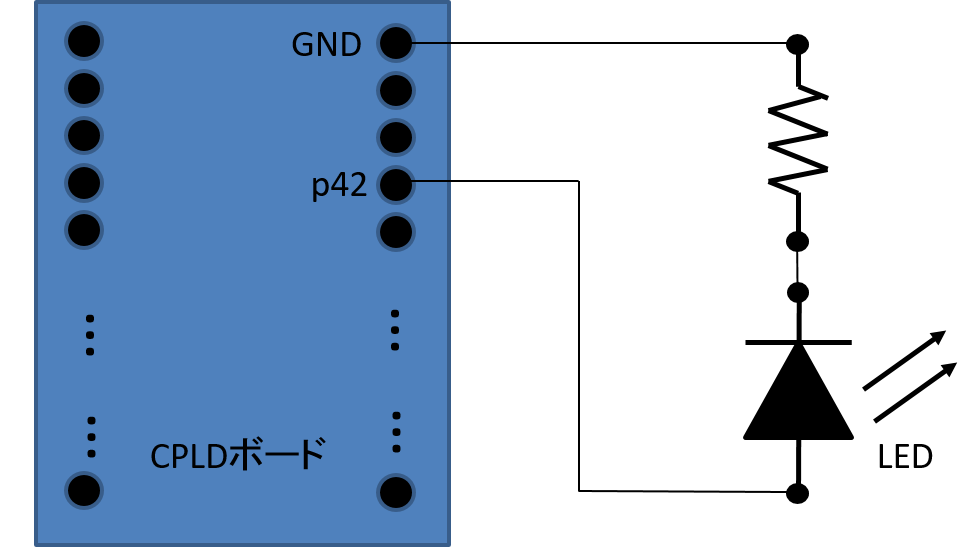

本例題では、p42ピンの電圧(0Vまたは+5Vの論理)を制御することで LEDを発光させる。 以下に示す回路をブレッドボード上に作成する。

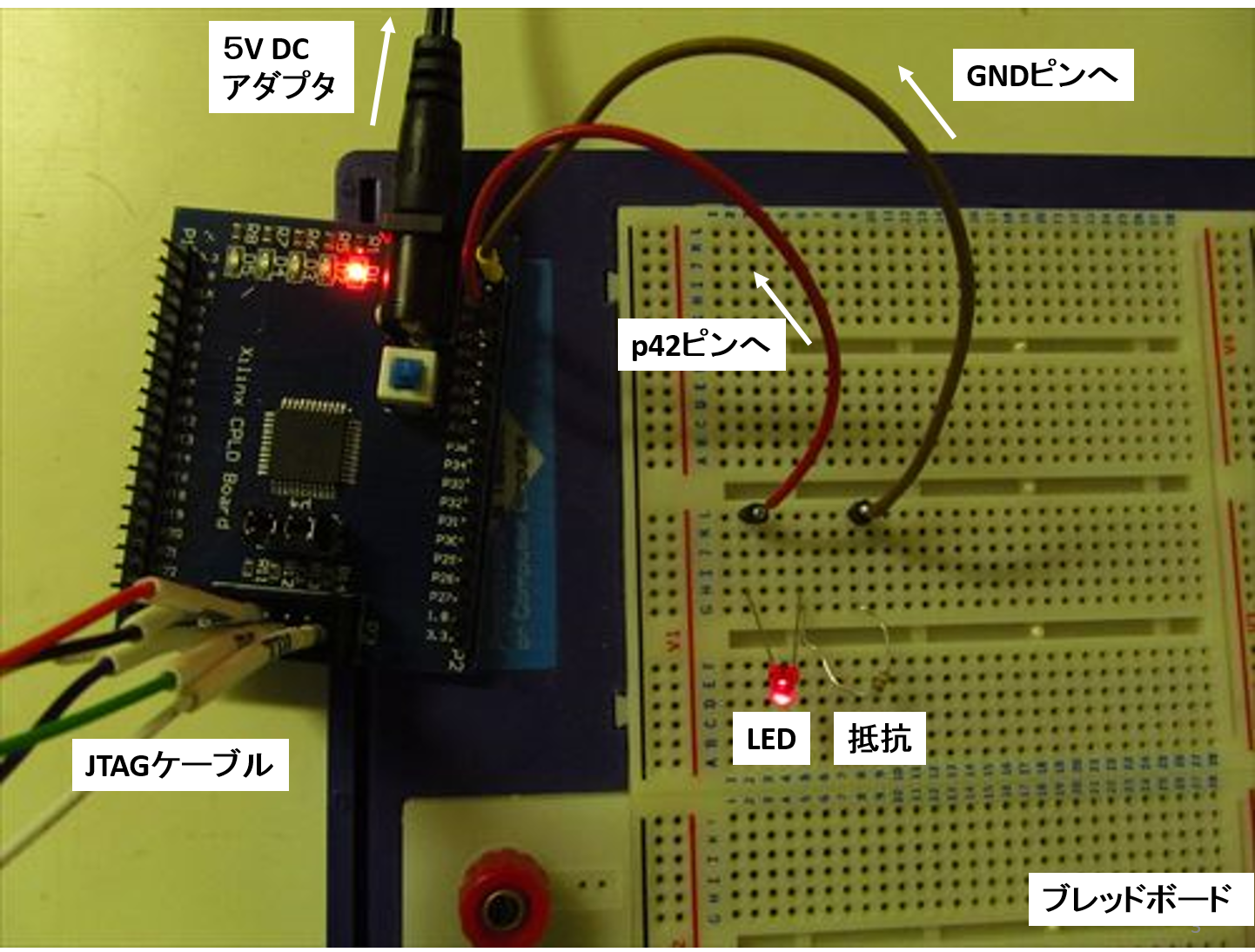

JTAGとLED周りの配線の全体像を以下写真に示すので参考にしてほしい。

抵抗はあまり大きな値のものを使用するとLEDを光らせるのに十分な電流が流れないので注意すること。

1kオーム程度の抵抗でよい。

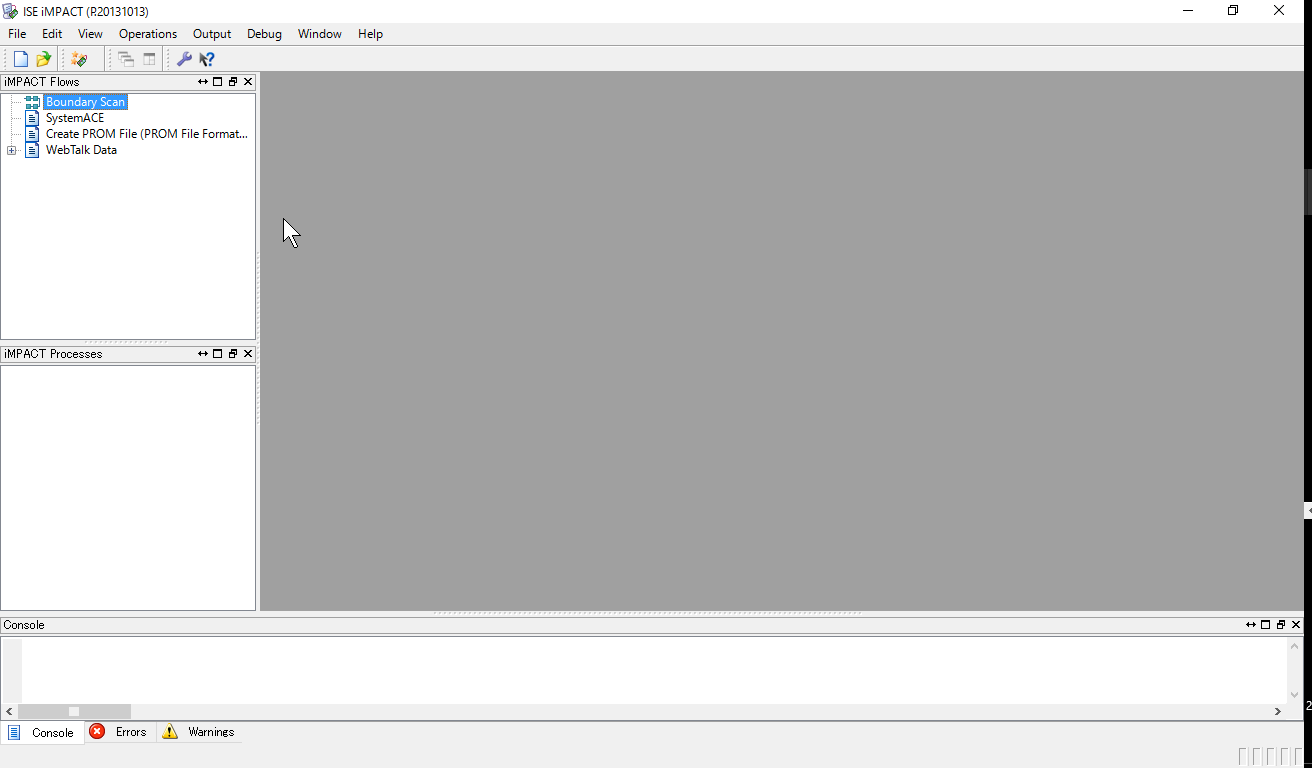

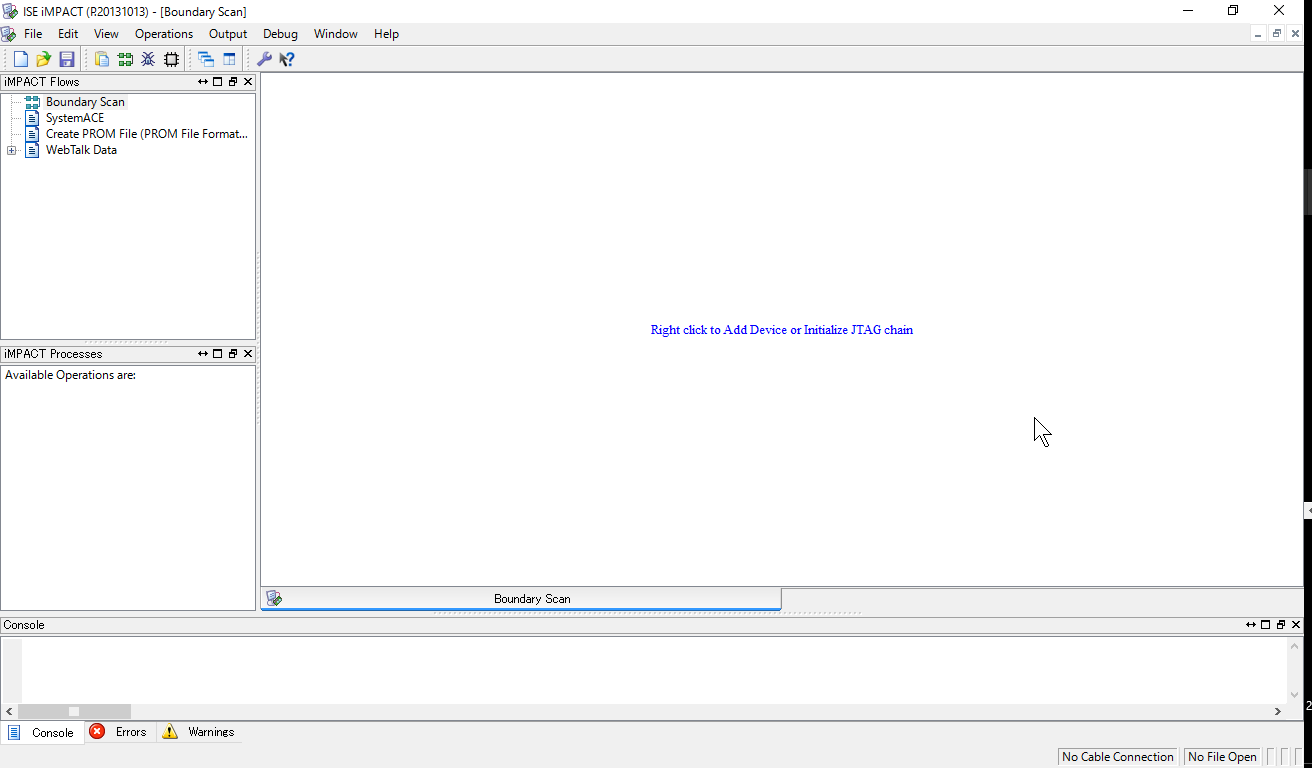

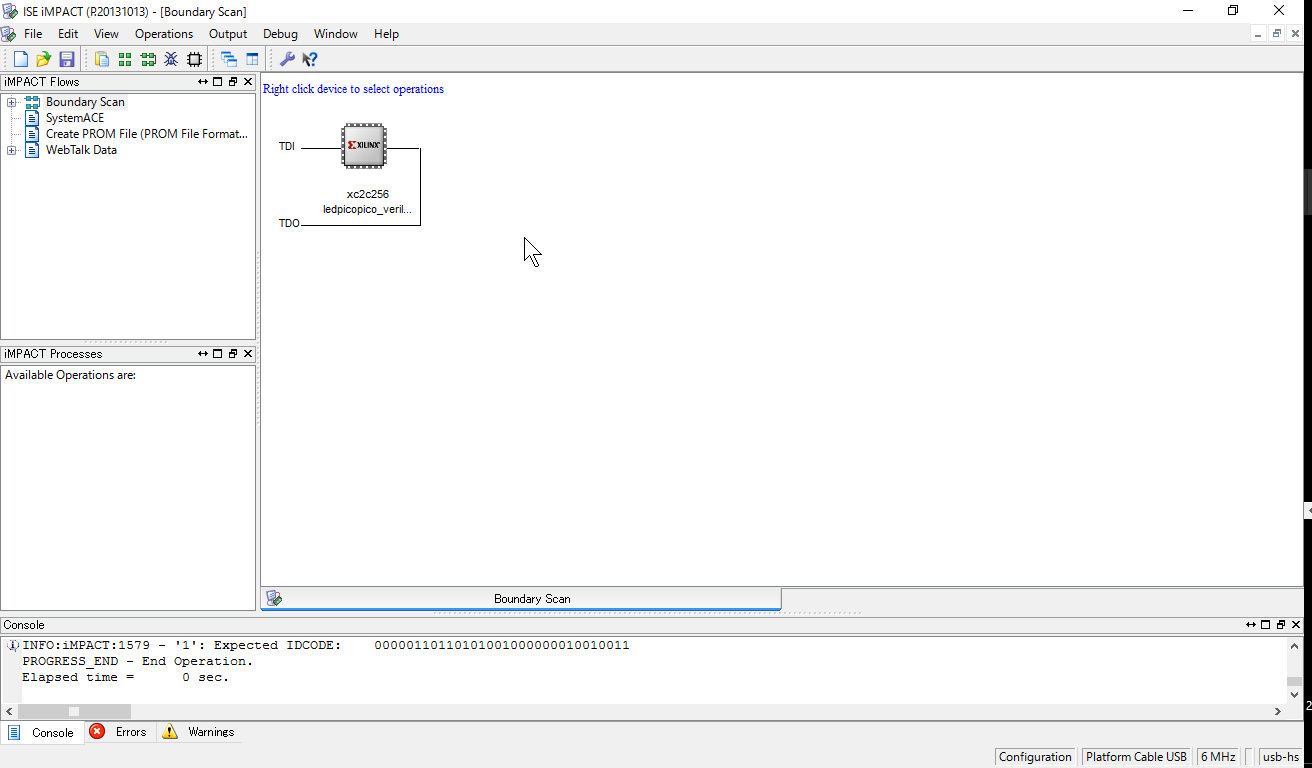

右フィールドに"Right Click to Add Device or Initialize JTAG chain"と でる。 右クリックし、"Add Xilinx Device..."を選択。

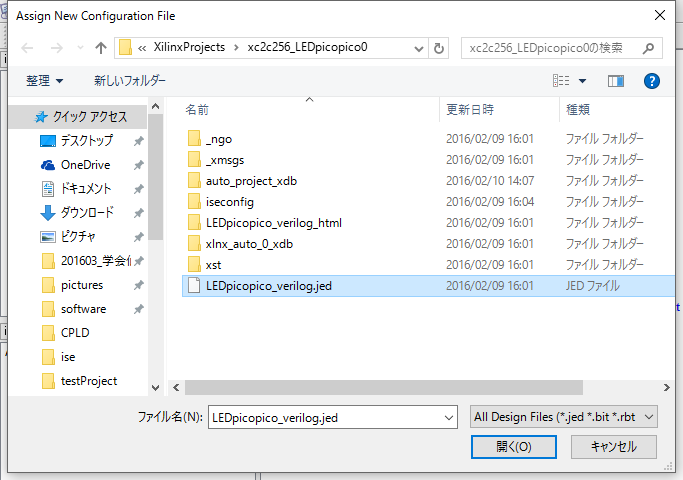

ISE navigatorで作成してあった .jed ファイルを選択する。

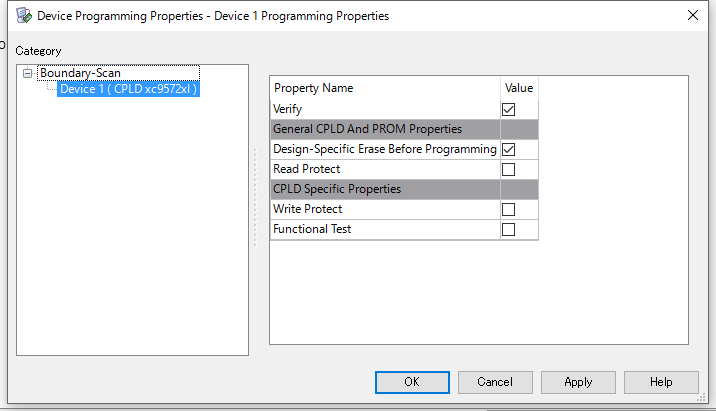

チップのアイコンを右クリックし、"Program"を実行。

ポップアップするオプションは変更の必要なし。

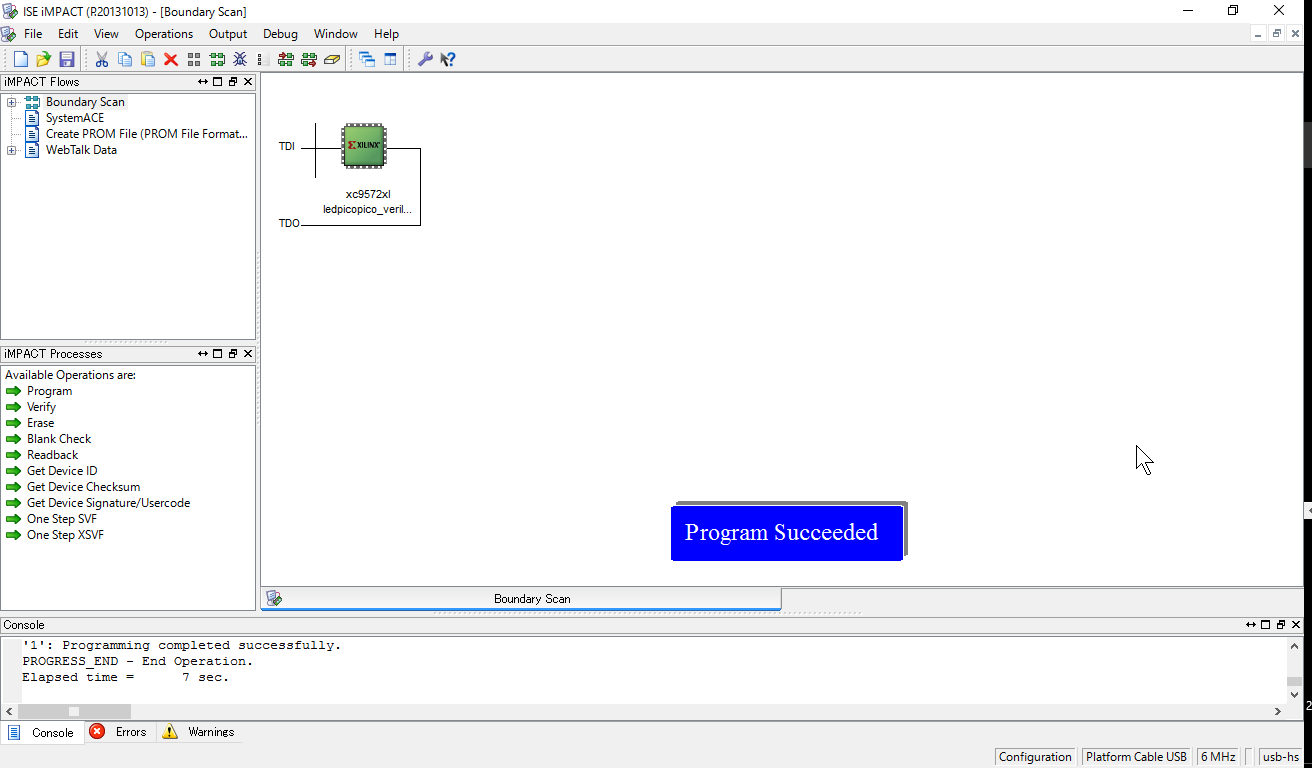

書き込みが成功すれば、"Program Succeeded"となり、ICはユーザが設計した通りの動作をはじめる。

なお、いったん書き込みが成功したら、次にJTAGからのアクセスが行われるまで

ICに実現された回路は保持される。

ボードの電源を切っても、再び電源を入れれば、同じ動作をすることを確認しよう。

いったん書き込みが終わったら、JTAGケーブルをはずしても大丈夫なことを確認しよう。

以上で、verilogによる回路設計から、それをICに書き込むまでの行程を一通り 行った。 ブレッドボード上のLEDが点灯を繰り返していれば成功である。

最後に、ここで扱ったverilogコードを解説する。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 13:05:18 05/17/2016

// Design Name:

// Module Name: LEDpicopico

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LEDpicopico_verilog(

input CLK,

output LEDdrv);

integer COUNTER;

always @ (posedge CLK) begin

if (COUNTER==250000000) begin

COUNTER <= 0;

end else begin

COUNTER <= COUNTER +1;

end

end

assign LEDdrv= (COUNTER<50000000);

endmodule

verilogではmoduleからendmoduleの間でモジュールの定義を行う。 したがって、本例題は一つのモジュール LEDpicopico_verilog を実装している。

モジュールの引数には (input CLK, output LEDdrv) としている。

ここでは、CLK、LEDdrvはICへのI/O(入出力信号)であり、

.ucfファイル内でそれぞれp1とp42ピンをアサインした。

NET "CLK" LOC = "P1";

NET "LEDdrv" LOC = "P42";

verilogでは、整数型integerの変数が定義されており、ここでもCOUNTERは整数型変数として定義した。

"always @ (posedge CLK) begin ... end"の部分は、クロック信号CLKの立ち上がりを検出したら、 そのたびに ... の処理を行う。

if (COUNTER==250000000) begin

COUNTER <= 0;

end else begin

COUNTER <= COUNTER +1;

end

assign LEDdrv= (COUNTER<50000000);

実際のLEDの動作がその通りかどうか、確かめよう。

また、コード中の250000000や50000000を別の数字に変えてコンパイル、実装して、

LED発光のパターンを自分で変更してみよう。

まずは、verilog言語での回路記述の基礎を学んでみよう。

たとえば、

http://research.kek.jp/people/uchida/educations/verilogHDL/introduction-to-veriloghdl.pdf

は、非常に簡潔に基礎的なことが学べるようにまとまっている。

もちろん、書籍もたくさん出版されているようです。

PLDやほかの論理ICの歴史的背景、現状に興味があったら、

ザイリンクスFPGA講座

を読んでみよう。

1-2章では論理ICの概説がわかりやすく解説されている。

また、3-4章にはISEの使用の仕方について概説してあり、

本ページの作成には大変参考になった。

JTAGのピン配置については、以下のページの解説を参考にした。

http://www2.tokudenkairo.co.jp/jtag/jtagpin.html

本授業では、日昇テクノロジー社製 Xilinx XC9572XL CPLD開発キットを教材として用いる。

この製品についてのマニュアル、データシート等、あらゆる詳細は以下のページからダウンロードできる。

http://www.csun.co.jp/SHOP/2011090801.html